# NMOS linear image sensor \$3902/\$3903 series

Current output, high UV sensitivity, excellent linearity, low power consumption

NMOS linear image sensors are self-scanning photodiode arrays designed specifically as detectors for multichannel spectroscopy. The scanning circuit is made up of N-channel MOS transistors, operates at low power consumption and is easy to handle. Each photodiode has a large active area, high UV sensitivity yet very low noise, delivering a high S/N even at low light levels. NMOS linear image sensors also offer excellent output linearity and wide dynamic range.

The photodiodes of S3902 series have a height of 0.5 mm and are arrayed in a row at a spacing of 50 µm. The photodiodes of S3903 series also have a height of 0.5 mm but are arrayed at a spacing of 25 µm. The photodiodes are available in 3 different pixel quantities for each series: 128 (S3902-128Q), 256 (S3902-256Q, S3903-256Q), 512 (S3902-512Q, S3903-512Q) and 1024 (S3903-1024Q). Quartz glass is the standard window material.

#### **Features**

Wide active area

Pivol pitch: 50 um (\$300)

Pixel pitch: 50 µm (S3902 series) 25 µm (S3903 series)

Pixel height: 0.5 mm

- High UV sensitivity with good stability

- Low dark current and high saturation charge allow a long integration time and a wide dynamic range at room temperature

- Excellent output linearity and sensitivity spatial uniformity

- Lower power consumption: 1 mW max.

- Start pulse and clock pulses are CMOS logic compatible

# Applications

- Multichannel spectrophotometry

- Image readout system

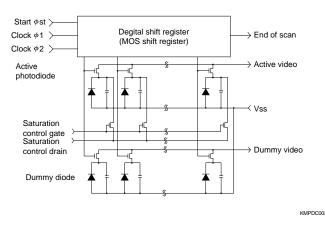

# ■ Equivalent circuit

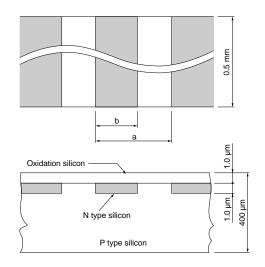

#### Active area structure

S3902 series: a=50  $\mu$ m, b=45  $\mu$ m S3903 series: a=25  $\mu$ m, b=20  $\mu$ m

KMPDA0107EA

## ■ Absolute maximum ratings

| Absolute maximum ratings             |        |            |      |  |  |  |  |

|--------------------------------------|--------|------------|------|--|--|--|--|

| Parameter                            | Symbol | Value      | Unit |  |  |  |  |

| Input pulse (\$1, \$2, \$st) voltage | Vφ     | 15         | V    |  |  |  |  |

| Power consumption*1                  | Р      | 1          | mW   |  |  |  |  |

| Operating temperature*2              | Topr   | -40 to +65 | °C   |  |  |  |  |

| Storage temperature                  | Tstg   | -40 to +85 | °C   |  |  |  |  |

<sup>\*1:</sup> V<sub>0</sub>=5.0 V

SOLID STATE DIVISION

<sup>\*2:</sup> No condensation

# NMOS linear image sensor \$3902/\$3903 series

■ Shape specifications

| Parameter        | S3902-<br>128Q | S3902-<br>256Q | S3902-<br>512Q | S3903-<br>256Q | S3903-<br>512Q | S3903-<br>1024Q | Unit |

|------------------|----------------|----------------|----------------|----------------|----------------|-----------------|------|

| Number of pixels | 128            | 256            | 512            | 256            | 512            | 1024            | -    |

| Package length   | 31.75          |                | 40.6           | 31.75          |                | 40.6            | mm   |

| Number of pin    | 22             |                | 22             |                |                | -               |      |

| Window material  | Quartz         |                |                | Quartz         |                |                 | -    |

| Weight           | 3              | .0             | 3.5            | 3.             | .0             | 3.5             | g    |

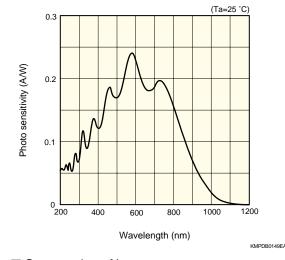

■ Specifications (Ta=25 °C)

| Parameter                             | Symbol | 5           | 3902 serie | S           | S3903 series |      |      | Unit          |

|---------------------------------------|--------|-------------|------------|-------------|--------------|------|------|---------------|

| Parameter                             |        | Min.        | Тур.       | Max.        | Min.         | Тур. | Max. | Utill         |

| Pixel pitch                           | -      | -           | 50         | -           | -            | 25   | -    | μm            |

| Pixel height                          | -      | -           | 0.5        | -           | -            | 0.5  | -    | mm            |

| Spectral response range (10% of peak) | λ      | 200 to 1000 |            | 200 to 1000 |              |      | nm   |               |

| Peak sensitivity wavelength           | λр     | -           | 600        | -           | -            | 600  | -    | nm            |

| Photodiode dark current*3             | ΙD     | -           | 0.08       | 0.15        | -            | 0.04 | 0.08 | pA            |

| Photodiode capacitance*3              | Cph    | -           | 4          | -           | -            | 2    | -    | pF            |

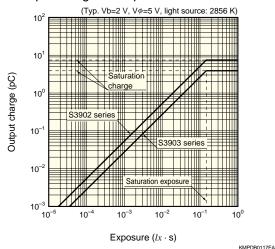

| Saturation exposure*3 *4              | Esat   | -           | 180        | -           | -            | 180  | -    | $mlx \cdot s$ |

| Saturation output charge*3            | Qsat   | -           | 10         | -           | -            | 5    | -    | pC            |

| Photo response non-uniformity*5       | PRNU   | -           | -          | ±3          | -            | -    | ±3   | %             |

<sup>\*3:</sup> Vb=2.0 V, V $\phi$ =5.0 V

■ Electrical characteristics (Ta=25 °C)

| Parameter                                                    |                                | Symbol                   | Condition           | S3902 series |                  |          | S3903 series |               |          | Unit  |

|--------------------------------------------------------------|--------------------------------|--------------------------|---------------------|--------------|------------------|----------|--------------|---------------|----------|-------|

| Falametei                                                    |                                |                          |                     | Min.         | Typ.             | Max.     | Min.         | Тур.          | Max.     | Offit |

| Clock pulse (\phi1, \phi2)                                   | High                           | V                        | -                   | 4.5          | 5                | 10       | 4.5          | 5             | 10       | V     |

| voltage                                                      |                                | V                        | -                   | 0            | -                | 0.4      | 0            | -             | 0.4      | V     |

| Start pulse (Act) voltage                                    | High                           | V                        | -                   | 4.5          | V <sub>0</sub> 1 | 10       | 4.5          | Vø1           | 10       | V     |

| Start pulse (\psi) voltage                                   | Low                            | V                        | -                   | 0            | -                | 0.4      | 0            | -             | 0.4      | V     |

| Video bias voltage*6                                         |                                | Vb                       | -                   | 1.5          | V  - 3.0         | Vø - 2.5 | 1.5          | V  - 3.0      | Vø - 2.5 | V     |

| Saturation control gate volta                                | age                            | Vscg                     | -                   | -            | 0                | -        | -            | 0             | -        | V     |

| Saturation control drain volt                                | age                            | Vscd                     | -                   | ı            | Vb               | -        | -            | Vb            | -        | V     |

| Clock pulse (φ1, φ2) rise / fall time*7                      |                                | trø1, trø2<br>tfø1, tfø2 | -                   | ı            | 20               | ı        | ı            | 20            | -        | ns    |

| Clock pulse (\$1, \$2) pulse wi                              | dth                            | tpwφ1, tpwφ2             | -                   | 200          | -                | -        | 200          | -             | -        | ns    |

| Start pulse (ost) rise / fall tir                            | ne                             | trφs, tfφs               | -                   | -            | 20               | -        | -            | 20            | -        | ns    |

| Start pulse (\( \psi 1, \( \phi 2 \)) pulse width            |                                | tpwφs                    | -                   | 200          | -                | -        | 200          | -             | -        | ns    |

| Start pulse (\$\psi\$st) and clock pulse (\$\psi\$2) overlap |                                | tφον                     | -                   | 200          | -                | -        | 200          | -             | -        | ns    |

| Clock pulse space*7                                          |                                | X1, X2                   | -                   | trf - 20     | -                | -        | trf - 20     | -             | -        | ns    |

| Data rate*8                                                  |                                | f                        | -                   | 0.1          | -                | 2000     | 0.1          | -             | 2000     | kHz   |

|                                                              |                                |                          | 50% of              | -            | 70 (-128 Q)      | -        | -            | 80 (-256 Q)   | -        | ns    |

| Video delay time                                             |                                | tvd                      | saturation<br>*8 *9 | •            | 110 (-256 Q)     | -        | -            | 120 (-512 Q)  | -        | ns    |

|                                                              |                                |                          |                     | ı            | 140 (-512 Q)     | -        | -            | 160 (-1024 Q) | -        | ns    |

| Clock pulse (\phi1, \phi2)                                   | Cleak mules (±1 ±2)            |                          |                     | -            | 21 (-128 Q)      | -        | -            | 27 (-256 Q)   | -        | pF    |

| line capacitance                                             |                                | Сф                       | 5 V bias            | -            | 36 (-256 Q)      | -        | -            | 50 (-512 Q)   | -        | pF    |

| ппе сараспансе                                               |                                |                          |                     | -            | 67 (-512 Q)      | -        | -            | 100 (-1024 Q) | -        | pF    |

| Saturation control gate (Vsc                                 | Saturation control date (Vscd) |                          |                     | -            | 12 (-128 Q)      | -        | -            | 12 (-256 Q)   | -        | pF    |

| line capacitance                                             | -3/                            | Cscg                     | 5 V bias            | -            | 20 (-256 Q)      | -        | -            | 24 (-512 Q)   | -        | pF    |

|                                                              |                                |                          |                     | -            | 35 (-512 Q)      | -        | -            | 45 (-1024 Q)  | -        | pF    |

| V() 1                                                        |                                |                          | 0 ) / 1 :           | -            | 7 (-128 Q)       | -        | -            | 10 (-256 Q)   | -        | pF    |

| Video line capacitance                                       |                                | Cv 2                     | 2 V bias            | -            | 11 (-256 Q)      | -        | -            | 16 (-512 Q)   | -        | pF    |

|                                                              |                                |                          |                     | -            | 20 (-512 Q)      | -        | -            | 30 (-1024 Q)  | -        | pF    |

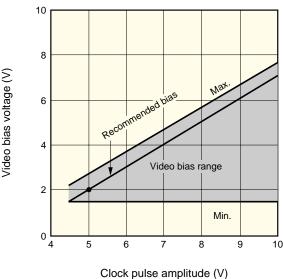

<sup>\*6:</sup> Vo is input pulse voltage (refer to "■ Video bias voltage margin")

<sup>\*4: 2856</sup> K, tungsten lamp

<sup>\*5: 50%</sup> of saturation, excluding the start pixel and last pixel

<sup>\*7:</sup> trf is the clock pulse rise or fall time. A clock pulse space of "rise time/fall time - 20" ns (nanoseconds) or more should be input if the clock pulse rise or fall time is longer than 20 ns. (refer to "■ Timing chart for driver circuit")

<sup>\*8:</sup> Vb=2.0 V, V $\phi$ =5.0 V

<sup>\*9:</sup> Measured with C7883 driver circuit.

# NMOS linear image sensor S3902/S3903 series

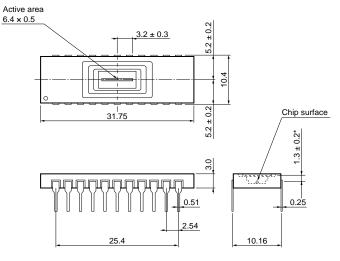

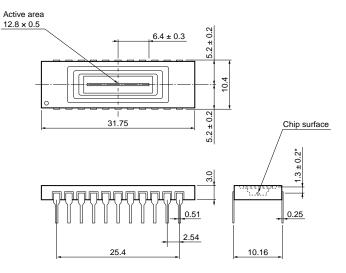

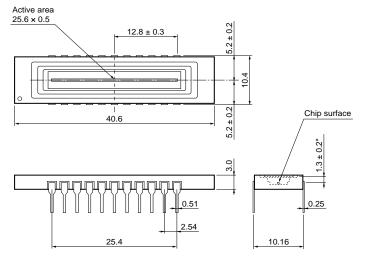

# ■ Dimensional outlines (unit: mm)

# S3902-128Q, S3903-256Q

\* Optical distance from the outer surface of the quartz window to the chip surface

# S3902-256Q, S3903-512Q

\* Optical distance from the outer surface of the quartz window to the chip surface

KMPDA0108EB

# S3902-512Q, S3903-1024Q

\* Optical distance from the outer surface of the quartz window to the chip surface

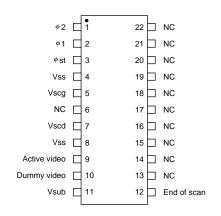

■ Pin connection

$\label{eq:Vss} \textit{Vss}, \textit{Vsub} \ \textit{and} \ \textit{NC} \ \textit{should} \ \textit{be} \ \textit{grounded}.$

KMPDC0056EA

KMPDA0109FB

KMPDA0110EB

# NMOS linear image sensor S3902/S3903 series

| Terminal     | Input or output                   | Description                                                                                                                                                                                                                                                                             |  |  |  |  |

|--------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| φ1, φ2       | Input<br>(CMOS logic compatible)  | Pulses for operating the MOS shift register. The video data rate is equal to the clock pulse frequency since the video output signal is obtained synchronously with the rise of φ2 pulse.                                                                                               |  |  |  |  |

| φst          | Input (CMOS logic compatible)     | Pulse for starting the MOS shift register operation. The time interval between start pulses is equal to the signal accumulation time.                                                                                                                                                   |  |  |  |  |

| Vss          | -                                 | Connected to the anode of each photodiode. This should be grounded.                                                                                                                                                                                                                     |  |  |  |  |

| Vscg         | Input                             | Used for restricting blooming. This should be grounded.                                                                                                                                                                                                                                 |  |  |  |  |

| Vscd         | Input                             | Used for restricting blooming. This should be biased at a voltage equal to the video bias voltage.                                                                                                                                                                                      |  |  |  |  |

| Active video | Output                            | Video output signal. Connects to photodiode cathodes when the address is on. A positive voltage should be applied to the video line in order to use photodiodes with a reverse voltage. When the amplitude of $\phi 1$ and $\phi 2$ is 5 V, a video bias voltage of 2 V is recommended. |  |  |  |  |

| Dummy video  | Output                            | This has the same structure as the active video, but is not connected to photodiodes, so only spike noise is output. This should be biased at a voltage equal to the active video or left as an open-circuit when not needed.                                                           |  |  |  |  |

| Vsub         | -                                 | Connected to the silicon substrate. This should be grounded.                                                                                                                                                                                                                            |  |  |  |  |

| End of scan  | Output<br>(CMOS logic compatible) | This should be pulled up at 5 V by using a 10 k $\Omega$ resistor. This is a negative going pulse that appears synchronously with the $\phi 2$ timing right after the last photodiode is addressed.                                                                                     |  |  |  |  |

| NC           | -                                 | Should be grounded.                                                                                                                                                                                                                                                                     |  |  |  |  |

## ■ Spectral response (typical example)

# ■ Construction of image sensor

The NMOS image sensor consists of a scanning circuit made up of MOS transistors, a photodiode array, and a switching transistor array that addresses each photodiode, all integrated onto a monolithic silicon chip. "Equivalent circuit" shows the circuit of a NMOS linear image sensor.

The MOS scanning circuit operates at low power consumption and generates a scanning pulse train by using a start pulse and 2-phase clock pulses in order to turn on each address sequentially. Each address switch is comprised of an NMOS transistor using the photodiode as the source, the video line as the drain and the scanning pulse input section as the gate.

The photodiode array operates in charge integration mode so that the output is proportional to the amount of light exposure (light intensity x integration time).

Each cell consists of an active photodiode and a dummy

## Output charge vs. exposure

photodiode, which are respectively connected to the active video line and the dummy video line via a switching transistor. Each of the active photodiodes is also connected to the saturation control drain via the saturation control transistor, so that the photodiode blooming can be suppressed by grounding the saturation control gate. Applying a pulse signal to the saturation control gate triggers all reset. (See

"■Auxiliary functions".)

"■Active area structure" shows the schematic diagram of the photodiode active area. This active area has a PN junction consisting of an N-type diffusion layer formed on a P-type silicon substrate. A signal charge generated by light input accumulates as a capacitive charge in this PN junction. The N-type diffusion layer provides high UV sensitivity but low dark current.

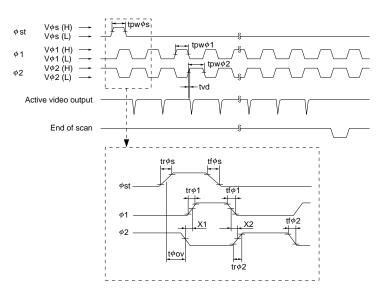

#### ■ Driver circuit

S3902/S3903 series do not require any DC voltage supply for operation. However, the Vss, Vsub and all NC terminals must be grounded. A start pulse  $\phi st$  and 2-phase clock pulses  $\phi 1, \phi 2$  are needed to drive the shift register. These start and clock pulses are positive going pulses and CMOS logic compatible. The 2-phase clock pulses  $\phi 1, \phi 2$  can be either completely separated or complementary. However, both pulses must not be "High" at the same time.

A clock pulse space (X1 and X2 in "■Timing chart for driver circuit") of a "rise time/fall time - 20" ns or more should be input if the rise and fall times of φ1, φ2 are longer than 20 ns. The φ1 and φ2 clock pulses must be held at "High" at least 200 ns. Since the photodiode signal is obtained at the rise of each φ2 pulse, the clock pulse frequency will equal the video data rate. The amplitude of start pulse φst is the same as the φ1 and φ2

pulses. The shift register starts the scanning at the "High" level of φst, so the start pulse interval determines the length of signal accumulation time. The φst pulse must be held "High" at least 200 ns and overlap with φ2 at least for 200 ns. To operate the shift register correctly, φ2 must change from the "High" level to the "Low" level only once during "High" level of φst. The timing chart for each pulse is shown in "■Timing chart for driver circuit".

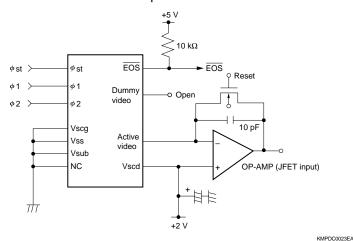

#### ■ End of scan

The end of scan ( $\overline{EOS}$ ) signal appears in synchronization with the  $\phi2$  timing right after the last photodiode is addressed, and the  $\overline{EOS}$  terminal should be pulled up at 5 V using a 10 k $\Omega$  resistor.

# ■ Timing chart for driver circuit

#### ■ Signal readout circuit

There are two methods for reading out the signal from an NMOS linear image sensor. One is a current detection method using the load resistance and the other is a current integration method using a charge amplifier. In either readout method, a positive bias must be applied to the video line because photodiode anodes of NMOS linear image sensors are set at 0 V (Vss).

"■Video bias voltage margin" shows a typical video bias voltage margin. As the clock pulse amplitude is higher, the video bias voltage can be set larger so the saturation charge can be increased. The rise and fall times of the video output waveform can be shortened if the video bias voltage is reduced while the clock pulse amplitude is still higher. When the amplitude of  $\phi 1$ ,  $\phi 2$  and  $\phi st$  is 5 V, setting the video bias voltage at 2 V is recommended.

To obtain good linearity, using the current integration method is advised. In this method, the integration capacitance is reset to the reference voltage level immediately before each photodiode is addressed and the signal charge is then stored as an integration capacitive charge when the address switch turns on.

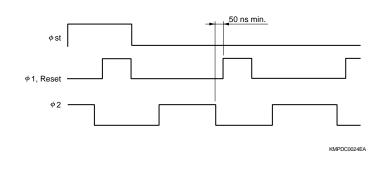

"■Readout circuit example" and "■Timing chart" show a typical current integration circuit and its pulse timing chart. To ensure stable output, the rise of a reset pulse must be delayed at least 50 ns from the fall of 62.

# ■ Video bias voltage margin

KMPDC0022E4

Hamamatsu provides the following driver circuits and related products (sold separately).

| Product name    | Type no.  | Content                       | Feature                                  |  |  |

|-----------------|-----------|-------------------------------|------------------------------------------|--|--|

|                 | C7883     | High-speed driver circuit     | High-speed operation Single power supply |  |  |

|                 | C7883G    | C7883<br>+ C8225-01           | (+15 V) operation<br>Compact             |  |  |

| Driver          | C7884     | Precision driver circuit      | Low noise<br>Good output linearity       |  |  |

| circuit         | C7884G    | C7884<br>+ C8225-01           | Boxcar waveform output                   |  |  |

|                 | C7884-01  | High precision driver circuit | Ultra-low noise<br>Good output linearity |  |  |

|                 | C7884G-01 | C7884-01<br>+ C8225-01        | Boxcar waveform output                   |  |  |

| Pulse generator | C8225-01  | C7883,<br>C7884 series        |                                          |  |  |

| Cable A8226     |           | C7883 to<br>C7885 series      | BNC, length 1 m                          |  |  |

KMPDR0043E4

# NMOS linear image sensor S3902/S3903 series

# ■ Readout circuit example

# ■ Timing chart

# $10 \times 10^{-12}$ [F] shown in.

Output charge [C]

# ■ Anti-blooming function

Output voltage Vout is

Vout [V] =

If the incident light intensity is higher than the saturation charge level, even partially, a signal charge in excess of the saturation charge cannot accumulate in the photodiode. This excessive charge flows out into the video line degrading the signal purity. To avoid this problem and maintain the signal purity, applying the same voltage as the video bias voltage to the saturation control drain and grounding the saturation control gate are effective. If the incident light intensity is extremely high, a positive bias should be applied to the saturation control gate. The larger the voltage applied to the saturation control gate, the higher the function for suppressing the excessive saturation charge will be. However, this voltage also lowers the amount of saturation charge, so an optimum bias voltage should be selected.

#### Auxiliary functions

#### 1) All reset

In normal operation, the accumulated charge in each photodiode is reset when the signal is read out. Besides this method that uses the readout line, S3902/S3903 series can reset the photodiode charge by applying a pulse to the saturation control gate. The amplitude of this pulse should be equal to the  $\phi1$ ,  $\phi2$  and  $\phi$ st pulses and the pulse width should be longer than 5  $\mu$ s. When the saturation control gate is set at the "High" level, all photodiodes are reset to the saturation control drain potential (equal to video bias). Conversely, when the saturation control gate is set at the "Low" level (0 V), the signal charge accumulates in each photodiode without being reset.

## 2) Dummy video

S3902/S3903 series have a dummy video line to eliminate spike noise contained in the video output waveform. Video signal with lower spike noise can be obtained by differential amplification applied between the active video line and dummy video line outputs. When not needed, leave this unconnected.

## ■ Handling precautions

#### 1) Electrostatic countermeasures

NMOS linear image sensors are designed to resist static electrical charges. However, take sufficient cautions and countermeasures to prevent damage from static charges when handling the sensors.

## 2) Window

If dust or grime sticks to the surface of the light input window, it appears as a black blemish or smear on the image. Before using the image sensor, the window surface should be cleaned. Wipe off the window surface with a soft cloth, cleaning paper or cotton swab slightly moistened with organic solvent such as alcohol, and then lightly blow away with compressed air. Do not rub the window with dry cloth or cotton swab as this may generate static electricity.

# HAMAMATSU

Information furnished by HAMAMATSU is believed to be reliable. However, no responsibility is assumed for possible inaccuracies or omissions. Specifications are subject to change without notice. No patent rights are granted to any of the circuits described herein. Type numbers of products listed inthe specification sheets or supplied as samples may have a suffix "(X)" which means tentative specifications or a suffix "(Z)" which means developmental specifications. ©2010 Hamamatsu Photonics K.K.

HAMAMATSU PHOTONICS K.K., Solid State Division

1126-1 Ichino-cho, Higashi-ku, Hamamatsu City, 435-8558 Japan, Telephone: (81) 53-434-3311, Fax: (81) 53-434-5184, www.hamamatsu.com

U.S.A.: Hamamatsu Corporation: 360 Foothill Road, P.O.Box 6910, Bridgewater, N.J. 08807-0910, U.S.A., Telephone: (1) 908-231-0960, Fax: (1) 908-231-1218

Germany: Hamamatsu Photonics Deutschland GmbH: Arzbergerstr. 10, D-82211 Herrsching am Ammersee, Germany, Telephone: (49) 8152-375-0, Fax: (49) 8152-265-8

France: Hamamatsu Photonics France S.A.R.L.: 19, Rue du Saule Trapu, Parc du Moulin de Massy, 91882 Massy Cedex, France, Telephone: 33-(1) 69 53 71 00, Fax: 33-(1) 69 53 71 00, Fax