# NMOS linear image sensor \$5930/\$5931 series

Built-in thermoelectric cooler ensures long exposure time and stable operation.

NMOS linear image sensors are self-scanning photodiode arrays designed specifically as detectors for multichannel spectroscopy. The scanning circuit is made up of N-channel MOS transistors, operates at low power consumption and is easy to handle. Each photodiode has a large active area, high UV sensitivity yet very low noise. The built-in thermoelectric cooler (air cooled) allows a long exposure time achieving a high S/N even at low light levels. The cap uses a sapphire glass window hermetically welded for high reliability.

#### Features

Wide active area

Pixel pitch: 50 µm (S5930 series) 25 µm (S5931 series)

Pixel height: 2.5 mm

- High UV sensitivity with good stability

- Low dark current and high saturation charge allow a long integration time and a wide dynamic range at room temperature

- Excellent output linearity and sensitivity spatial uniformity

- Start pulse and clock pulses are CMOS logic compatible

- Built-in air-cooled thermoelectric cooler (setting temperature: 0 °C)

#### Applications

- Multichannel spectrophotometry

- Image readout system

■ Selection guide

| Type No.    | Number of pixels | Pixel size<br>[µm (H) × µm (V)] | Active area size<br>[mm (H) × mm (V)] |

|-------------|------------------|---------------------------------|---------------------------------------|

| S5930-256S  | 256              | 50 × 2500                       | 12.8 × 2.5                            |

| S5930-512S  | 512              | 50 ^ 2500                       | 25.6 × 2.5                            |

| S5931-512S  | 512              | 25 × 2500                       | 12.8 × 2.5                            |

| S5931-1024S | 1024             | 25 ^ 2500                       | 25.6 × 2.5                            |

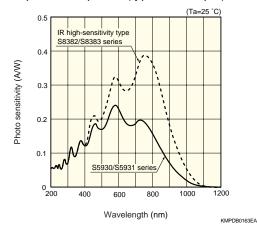

In addition to S5930/S5931 series, Hamamatsu provides S8382/S8383 series thermoelectrically cooled NMOS linear image sensors that offer higher sensitivity in the near IR range. Major characteristics of S8382/S8383 series are almost identical with S5930/S5931 series except that the peak sensitivity wavelength is 750 nm (see " $\blacksquare$  Spectral response") and the saturation charge is 90 m/ $\times$  s.

# NMOS linear image sensor \$5930/\$5931 series

#### ■ Equivalent circuit

# Start \$\phi\$\$ Clock \$\phi\$\$ 1 \quad Digital shift register (MOS shift register) \quad Active video \quad Active photodiode \quad \qu

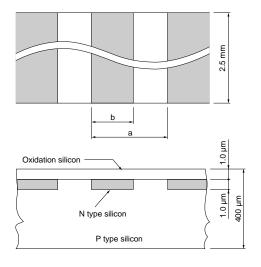

#### ■ Active area structure

S5930 series: a=50 μm, b=45 μm S5931 series: a=25 μm, b=20 μm

KMPDA0132EA

■ Absolute maximum ratings

| Parameter                                              | Symbol | Condition              | Value      | Unit |

|--------------------------------------------------------|--------|------------------------|------------|------|

| Input pulse (\$\phi1\$, \$\phi2\$, \$\phist\$) voltage | Vφ     |                        | 15         | V    |

| Operating temperature *1                               | Topr   | Ambient temperature *2 | -40 to +65 | °C   |

| Operating temperature                                  | Τορι   | Chip temperature       | -40 to +50 | °C   |

| Storage temperature                                    | Tstg   |                        | -40 to +85 | °C   |

KMPDC0020EA

■ Specifications (Ta=25 °C, unless otherwise noted)

| Parameter                             | Symbol | S5930 series |             |       | S5931 series |             |       | Unit          |

|---------------------------------------|--------|--------------|-------------|-------|--------------|-------------|-------|---------------|

| raiailletei                           |        | Min.         | Typ.        | Max.  | Min.         | Тур.        | Max.  | Offic         |

| Pixel pitch                           | -      | ı            | 50          | -     | ı            | 25          | -     | μm            |

| Pixel height                          | -      | -            | 2.5         | -     | -            | 2.5         | -     | mm            |

| Spectral response range (10% of peak) | λ      |              | 200 to 1000 | )     |              | 200 to 1000 | )     | nm            |

| Peak sensitivity wavelength           | λр     | -            | 600         | -     | -            | 600         | -     | nm            |

| Photodiode dark current *3 25 °C 0 °C | lo     | ı            | 0.2         | 0.6   | ı            | 0.1         | 0.3   | pА            |

| 0 °C                                  |        | •            | 0.006       | 0.018 | ı            | 0.003       | 0.009 |               |

| Photodiode capacitance *3             | Cph    | -            | 20          | -     | -            | 10          | -     | pF            |

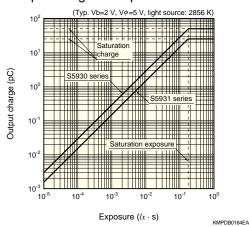

| Saturation exposure *3*4              | Esat   | -            | 180         | -     | -            | 180         | -     | $mlx \cdot s$ |

| Saturation output charge *3           | Qsat   | -            | 50          | -     | -            | 25          | -     | рC            |

| Photo response non-uniformity *5      | PRNU   | -            | -           | ±3    | -            | -           | ±3    | %             |

<sup>\*3:</sup> Vb=2.0 V, V $\phi$ =5.0 V

<sup>\*1:</sup> No condensation

<sup>\*2:</sup> The chip temperature should be monitored based on the thermistor resistance in order to keep the chip temperature within the rated range.

<sup>\*4: 2856</sup> K, tungsten lamp

<sup>\*5: 50%</sup> of saturation, excluding the start pixel and last pixel

# NMOS linear image sensor S5930/S5931 series

■ Electrical characteristics (Ta=25 °C)

| Parameter                                                      |      | Symbol                                 | Condition          | S5930 series |                  |          | S5931 series |                  |          | Unit  |

|----------------------------------------------------------------|------|----------------------------------------|--------------------|--------------|------------------|----------|--------------|------------------|----------|-------|

|                                                                |      | Symbol                                 |                    | Min.         | Тур.             | Max.     | Min.         | Typ.             | Max.     | Offic |

| Clock pulse (\phi1, \phi2)                                     | High | V <sub>0</sub> 1, V <sub>0</sub> 2 (H) |                    | 4.5          | 5                | 10       | 4.5          | 5                | 10       | V     |

| voltage                                                        | Low  | Vφ1, Vφ2 (L)                           |                    | 0            | -                | 0.4      | 0            | -                | 0.4      | V     |

| Start pulse (øst) voltage                                      | High | Vøs (H)                                |                    | 4.5          | V <sub>0</sub> 1 | 10       | 4.5          | V <sub>0</sub> 1 | 10       | V     |

| Start pulse (ψst) voltage                                      | Low  | Vos (L)                                |                    | 0            | -                | 0.4      | 0            | -                | 0.4      | V     |

| Video bias voltage*6                                           |      | Vb                                     |                    | 1.5          | Vφ - 3.0         | Vφ - 2.5 | 1.5          | Vφ - 3.0         | Vφ - 2.5 | V     |

| Saturation control gate volta                                  | age  | Vscg                                   |                    | -            | 0                | -        | -            | 0                | -        | V     |

| Saturation control drain volt                                  | age  | Vscd                                   |                    | -            | Vb               | -        | -            | Vb               | -        | V     |

| Clock pulse ( $\phi$ 1, $\phi$ 2) rise/fall time* <sup>7</sup> |      | trø1, trø2<br>tfø1, tfø2               |                    | -            | 20               | -        | -            | 20               | -        | ns    |

| Clock pulse (\phi1, \phi2) pulse with                          | dth  | tpw\phi1, tpw\phi2                     |                    | 200          | -                | -        | 200          | -                | -        | ns    |

| Start pulse (ost) rise/fall time                               | е    | trφs, tfφs                             |                    | -            | 20               | -        | •            | 20               | -        | ns    |

| Start pulse (\pst) pulse width                                 |      | tpwφs                                  |                    | 200          | -                | -        | 200          | -                | -        | ns    |

| Start pulse (\$\phi\$st) and clock pulse (\$\phi\$2) overlap   |      | tφον                                   |                    | 200          | -                | -        | 200          | -                | -        | ns    |

| Clock pulse space*7                                            |      | X1, X2                                 |                    | trf - 20     | -                | -        | trf - 20     | -                | -        | ns    |

| Data rate*8                                                    |      | f                                      |                    | 0.1          | -                | 2000     | 0.1          | -                | 2000     | kHz   |

|                                                                |      |                                        | 50 % of            | ı            | 120 (-256S)      | -        | ı            | 150 (-512S)      | -        | ns    |

| Video delay time                                               |      | tvd                                    | saturation<br>*8*9 | -            | 160 (-512S)      | -        | -            | 200 (-1024S)     | -        | ns    |

| Clock pulse (\phi1, \phi2)                                     |      | Сф                                     | 5 V bias           | -            | 36 (-256S)       | -        | •            | 50 (-512S)       | -        | pF    |

| line capacitance                                               |      | Сф                                     | 5 V Dias           | -            | 67 (-512S)       | -        | -            | 100 (-1024S)     | -        | pF    |

| Saturation control gate (Vsc                                   | g)   | Cscg                                   | 5 V bias           | -            | 20 (-256S)       | -        | -            | 24 (-512S)       | -        | pF    |

| line capacitance                                               |      | Oscg                                   | o v blas           | -            | 35 (-512S)       | -        | -            | 45 (-1024S)      | -        | pF    |

| Video line capacitance                                         |      | Cv                                     | 2 V bias           | -            | 11 (-256S)       | -        | -            | 16 (-512S)       | -        | pF    |

| video inte oupdoltarios                                        |      |                                        | L v blas           | -            | 20 (-512S)       | -        | -            | 30 (-1024S)      | -        | pF    |

<sup>\*6:</sup> V∮ is input pulse voltage.

#### ■ Dimensional outlines (unit: mm)

#### S5930-256S, S5931-512S S5930-512S, S5931-1024S 4.05 ± 0.4\*2 4.05 ± 0.4\*2 $14.99 \pm 0.25$ \_\_\_\_\_ 32.0 ± 0.3 40.64 ± 0.3 50.0 58.84 $7.65 \pm 0.5$ \*1: Thickness of sapphire glass \*2: Distance from the surface of sapphire glass to the chip surface \*1: Thickness of sapphire glass \*2: Distance from the surface of sapphire glass to the chip surface 2.54 2.54 27.94

KMPDA0089JB

KMPDA0090JB

<sup>\*7:</sup> trf is the clock pulse rise or fall time. A clock pulse space of "rise time/fall time - 20" ns (nanoseconds) or more should be input if the clock pulse rise or fall time is longer than 20 ns.

<sup>\*8:</sup> Vb=2.0 V, V $\phi$ =5.0 V

<sup>\*9:</sup> Measured with C7883 driver circuit.

# NMOS linear image sensor \$5930/\$5931 series

#### ■ Pin connection

Vss, Vsub and NC should be grounded. Electricity flows between the 20th pin and package metal.

KMPDC0115EA

| Terminal     | Input or output                   | Description                                                                                                                                                                                                                                                                               |

|--------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| φ1, φ2       | Input<br>(CMOS logic compatible)  | Pulses for operating the MOS shift register. The video data rate is equal to the clock pulse frequency since the video output signal is obtained synchronously with the rise of $\phi 2$ pulse.                                                                                           |

| φst          | Input (CMOS logic compatible)     | Pulse for starting the MOS shift register operation. The time interval between start pulses is equal to the signal accumulation time.                                                                                                                                                     |

| Vss          | i                                 | Connected to the anode of each photodiode. This should be grounded.                                                                                                                                                                                                                       |

| Vscg         | Input                             | Used for restricting blooming. This should be grounded.                                                                                                                                                                                                                                   |

| Vscd         | Input                             | Used for restricting blooming. This should be biased at a voltage equal to the video bias voltage.                                                                                                                                                                                        |

| Active video | Output                            | Video output signal. Connects to photodiode cathodes when the address is on. A positive voltage should be applied to the video line in order to use photodiodes with a reverse voltage. When the amplitude of \$\phi\$1 and \$\phi\$2 is 5 V, a video bias voltage of 2 V is recommended. |

| Dummy video  | Output                            | This has the same structure as the active video, but is not connected to photodiodes, so only spike noise is output. This should be biased at a voltage equal to the active video or left as an open-circuit when not needed.                                                             |

| Vsub         | i                                 | Connected to the silicon substrate. This should be grounded.                                                                                                                                                                                                                              |

| End of scan  | Output<br>(CMOS logic compatible) | This should be pulled up at 5 V by using a 10 k $\Omega$ resistor. This is a negative going pulse that appears synchronously with the $\phi 2$ timing right after the last photodiode is addressed.                                                                                       |

| NC           | -                                 | Should be grounded.                                                                                                                                                                                                                                                                       |

| TE-cooler    | Input                             | For sensor chip cooling                                                                                                                                                                                                                                                                   |

| Thermistor   | Output                            | For temperature control                                                                                                                                                                                                                                                                   |

#### ■ Spectral response (typical example)

#### ■ Output charge vs. exposure

#### ■ Driver circuit

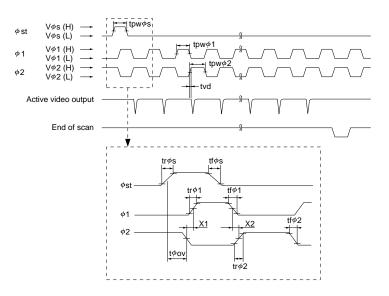

S5930/S5931 series do not require any DC voltage supply for operation. However, the Vss, Vsub and all NC terminals must be grounded. A start pulse  $\phi$ st and 2-phase clock pulses  $\phi$ 1,  $\phi$ 2 are needed to drive the shift register. These start and clock pulses are positive going pulses and CMOS logic compatible.

The 2-phase clock pulses  $\phi 1$ ,  $\phi 2$  can be either completely separated or complementary. However, both pulses must not be "High" at the same time.

A clock pulse space (X1 and X2 in "■Timing chart for driver circuit") of a "rise time/fall time - 20" ns or more should be input if the rise and fall times of φ1, φ2 are longer than 20 ns. The φ1 and φ2 clock pulses must be held at "High" at least 200 ns. Since the photodiode signal is obtained at the rise of each φ2 pulse, the clock pulse frequency will equal the video data rate.

#### ■ Timing chart for driver circuit

#### ■ Signal readout circuit

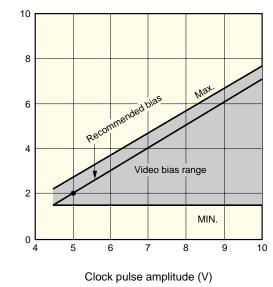

There are two methods for reading out the signal from an NMOS linear image sensor. One is a current detection method using the load resistance and the other is a current integration method using a charge amplifier. In either readout method, a positive bias must be applied to the video line because photodiode anodes of NMOS linear image sensors are set at 0 V (Vss). "■Video bias voltage margin" shows a typical video bias voltage margin. As the clock pulse amplitude is higher, the video bias voltage can be set larger so the saturation charge can be

bias voltage can be set larger so the saturation charge can be increased. The rise and fall times of the video output waveform can be shortened if the video bias voltage is reduced while the clock pulse amplitude is still higher. When the amplitude of  $\phi 1$ ,  $\phi 2$  and  $\phi st$  is 5 V, setting the video bias voltage at 2 V is recommended.

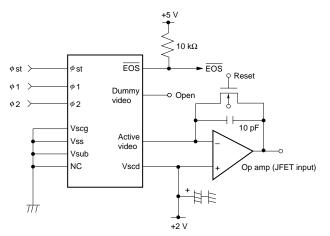

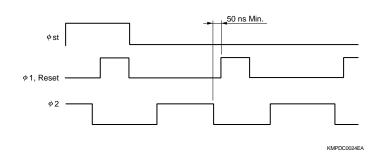

To obtain good linearity, using the current integration method is advised. In this method, the integration capacitance is reset to the reference voltage level immediately before each photodiode is addressed and the signal charge is then stored as an integration capacitive charge when the address switch turns on. "■Readout circuit example" and "■Timing chart" show a typi-

The amplitude of start pulse \$\phi\$st is the same as the \$\phi\$1 and \$\phi 2 pulses. The shift register starts the scanning at the "High" level of \$\phi\$st, so the start pulse interval determines the length of signal accumulation time. The \$\phi\$st pulse must be held "High" at least 200 ns and overlap with \$\phi\$2 at least for 200 ns. To operate the shift register correctly, \$\phi\$2 must change from the "High" level to the "Low" level only once during "High" level of \$\phi\$st. The timing chart for each pulse is shown in "■Timing chart for driver circuit".

#### ■ End of scan

Video bias voltage (V)

The end of scan (EOS) signal appears in synchronization with the  $\phi2$  timing right after the last photodiode is addressed, and the  $\overline{EOS}$  terminal should be pulled up at 5 V using a 10  $k\Omega$  resistor.

#### ■ Video bias voltage margin

cal current integration circuit and its pulse timing chart. To en-

sure stable output, the rise of a reset pulse must be delayed at least 50 ns from the fall of  $\phi$ 2.

5

#### ■ Readout circuit example

#### ■ Timing chart

KMPDC0023EA

Output voltage Vout is expressed by the following equation. Vout [V] =  $\frac{\text{Output charge [C]}}{10 \times 10^{-12} \text{ [F]}}$

#### ■ Anti-blooming function

If the incident light intensity is higher than the saturation charge level, even partially, a signal charge in excess of the saturation charge cannot accumulate in the photodiode. This excessive charge flows out into the video line degrading the signal purity. To avoid this problem and maintain the signal purity, applying the same voltage as the video bias voltage to the saturation control drain and grounding the saturation control gate are effective. If the incident light intensity is extremely high, a positive bias should be applied to the saturation control gate. The larger the voltage applied to the saturation control gate, the higher the function for suppressing the excessive saturation charge will be. However, this voltage also lowers the amount of saturation charge, so an optimum bias voltage should be selected.

#### Auxiliary functions

#### (1) All reset

In normal operation, the accumulated charge in each photodiode is reset when the signal is read out. Besides this method that uses the readout line, S5930/S5931 series can reset the photodiode charge by applying a pulse to the saturation control gate. The amplitude of this pulse should be equal to the  $\phi1$ ,  $\phi2$  and  $\phi$ st pulses and the pulse width should be longer than 5  $\mu$ s. When the saturation control gate is set at the "High" level, all photodiodes are reset to the saturation control drain potential (equal to video bias). Conversely, when the saturation control gate is set at the "Low" level (0 V), the signal charge accumulates in each photodiode without being reset.

#### (2) Dummy video

S5930/S5931 series have a dummy video line to eliminate spike noise contained in the video output waveform. Video signal with lower spike noise can be obtained by differential amplification applied between the active video line and dummy video line outputs. When not needed, leave this unconnected.

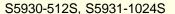

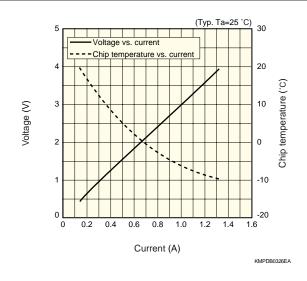

■ Specifications of built-in TE-cooler (Typ.)

| Parameter                      | Condition   | S5930-256S, S5931-512S | S5930-512S, S5931-1024S | Unit |

|--------------------------------|-------------|------------------------|-------------------------|------|

| Internal resistance            | Ta=25 °C    | 1.0                    | 1.3                     | Ω    |

| Maximum current*10             | Th=27 °C    | 2.8                    | 2.9                     | Α    |

| Maximum voltage*11             | Th=27 °C    | 3.5                    | 4.6                     | V    |

| Maximum heat absorption        | Tc=Th=27 °C | 6.0                    | 8.0                     | W    |

| Maximum temperature difference | Th=27 °C    | 67                     |                         | °C   |

| Maximum temperature of         |             | 8                      | °C                      |      |

| heat radiating side            |             | 0                      | 5                       |      |

<sup>\*10:</sup> Electrical current required to generate the maximum difference between temperatures (temperature Th on the heat radiating side and temperature Tc on the cooling side) at both ends of the thermoelectric cooler while heat is completely insulated. Cooling efficiency will drop if operated at a current higher than this value.

\*11: Voltage required for maximum current flow

<sup>\*12:</sup> Heat absorption amount when operated at maximum current. This is defined under the condition that the difference between the temperature Th on the heat radiating side and the temperature Tc on the cooling side is 0 °C.

#### S5930-256S, S5931-512S

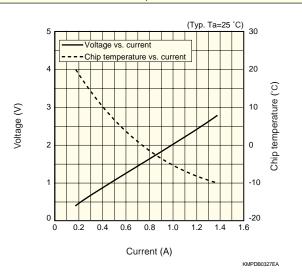

#### ■ Specifications of built-in temperature sensor

A thermistor chip is built in the same package with a NMOS chip, and the chip temperature can be monitored with it, A relation between the thermistor resistance and absolute temperature is expressed by the following equation.

$RT1 = RT2 \times exp BT1/T2 (1/T1 - 1/T2)$

RT1: Resistance at absolute temperature T1 [K] RT2: Resistance at absolute temperature T2 [K]

BT1/T2: B constant [K]

The characteristics of the thermistor used are as follows. R298=10  $k\Omega$

B298/323=3450 K

KMPDB0111EB

# NMOS linear image sensor S5930/S5931 series

#### Precautions

#### (1) Electrostatic countermeasures

This device has a built-in protection circuit against static electrical charges. However, to prevent destroying the device with electrostatic charges, take countermeasures such as grounding yourself, the workbench and tools to prevent static discharges. Also protect this device from surge voltages which might be caused by peripheral equipment.

#### (2) Light input window

If dust or dirt gets on the light input window, it will show up as black blemishes on the image. When cleaning, avoid rubbing the window surface with dry cloth or dry cotton swab, since doing so may generate static electricity. Use soft cloth, paper or a cotton swab moistened with alcohol to wipe dust and dirt off the window surface. Then blow compressed air onto the window surface so that no spot or stain remains.

#### (3) Soldering

To prevent damaging the device during soldering, take precautions to prevent excessive soldering temperatures and times. Soldering should be performed within 5 seconds at a soldering temperature below 260 °C.

#### (4) Precautions when mounting

When installing the device into the socket on the printed circuit board, insert it in the correct orientation after checking the pin connections. Also take measures to protect this device from static electricity during this work. Never press on the surface of the device when inserting it into the circuit board, etc. Pressing on the sensor surface causes cracks and fractures in the window, possibly causing it to fall out and may lead to malfunctions.

- Insert the sensor into the socket while pressing on the sensor edges as shown in photo 1 or pressing on the screw hole sections as shown in photo 2.

- · When securing the device by screws, place and secure it on a flat surface (flatness within 100 μm).

- Use a socket that matches the pin size and specifications.

Photo 2

Photo 1

#### (5) Operating and storage environments

Always observe the rated temperature range when handling the device. Operating or storing the device at an excessively high temperature and humidity may cause variations in performance characteristics and must be avoided.

#### (6) UV exposure

This device is designed to suppress performance deterioration due to UV exposure. Even so, avoid unnecessary UV exposure to the device.

#### NMOS multichannel detector head C5964 series

The C5964 series is a family of multichannel detectors developed for spectrophotometry in the UV to near infrared range (up to 1000 nm). The C5964 series device incorporates a thermoelectrically-cooled NMOS linear image sensor (S5930/S5931/S8382/S8383 series), low noise driver/amplifier circuit and highly stable temperature control circuit. It also operates from simple external signal inputs.

#### ■ Selection guide

The C5964 series consists of the following models depending on the NMOS linear image sensor used.

| NMOS                       | NMOS linear image sensor |                  |                                 |                                  |                  |  |  |  |  |

|----------------------------|--------------------------|------------------|---------------------------------|----------------------------------|------------------|--|--|--|--|

| multichannel detector head | Type no.                 | Number of pixels | Pixel size<br>[μm (H) × μm (V)] | Active area<br>[mm (H) × mm (V)] | Remark           |  |  |  |  |

| C5964-0800                 | S5930-256S               | 256              | 50 × 2500                       | $12.8 \times 2.5$                |                  |  |  |  |  |

| C5964-0900                 | S5930-512S               | 512              | 30 × 2300                       | $25.6 \times 2.5$                | Standard type    |  |  |  |  |

| C5964-0910                 | S5931-512S               | 512              | 25 × 2500                       | $12.8 \times 2.5$                | Standard type    |  |  |  |  |

| C5964-1010                 | S5931-1024S              | 1024             | 25 × 2500                       | 25.6 × 2.5                       |                  |  |  |  |  |

| C5964-0901                 | S8382-512S               | 512              | 50 × 2500                       | $25.6 \times 2.5$                | IR-enhanced type |  |  |  |  |

| C5964-1011                 | S8383-1024S              | 1024             | 25 × 2500                       | 25.6 × 2.5                       | ik-ennanced type |  |  |  |  |

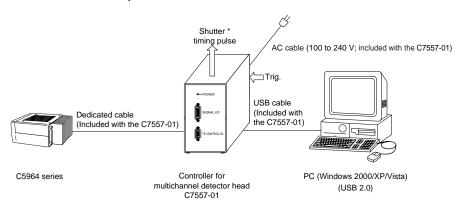

#### Multichannel detector head montroller C7557-01

The C7557-01 is specifically designed for basic control in multichannel photometry. When connected to a HAMAMATSU multichannel detector head and a personal computer, the C7557-01 allows easy control of the detector head and data acquisition by using dedicated software that comes with the unit.

#### ■ Connection example

\* Shutter, etc. are not available.

KACCC0070ED

Information described in this material is current as of August, 2014.

Product specifications are subject to change without prior notice due to improvements or other reasons. This document has been carefully prepared and the information contained is believed to be accurate. In rare cases, however, there may be inaccuracies such as text errors. Before using these products, always contact us for the delivery specification sheet to check the latest specifications.

The product warranty is valid for one year after delivery and is limited to product repair or replacement for defects discovered and reported to us within that one year period. However, even if within the warranty period we accept absolutely no liability for any loss caused by natural disasters or improper product

Copying or reprinting the contents described in this material in whole or in part is prohibited without our prior permission.

### HAMAMATSU

www.hamamatsu.com

HAMAMATSU PHOTONICS K.K., Solid State Division

1126-1 Ichino-cho, Higashi-ku, Hamamatsu City, 435-8558 Japan, Telephone: (81) 53-434-3311, Fax: (81) 53-434-5184

U.S.A.: Hamamatsu Corporation: 360 Foothill Road, Bridgewater, N.J. 08807, U.S.A.; Telephone: (1) 908-231-1960, Fax: (1) 908-231-1218

Germany: Hamamatsu Photonics Deutschland GmbH: Arzbergerstr. 10, D-82211 Herrsching am Ammersee, Germany, Telephone: (49) 8152-375-0, Fax: (49) 8152-265-8

France: Hamamatsu Photonics Trance S.A.R.L.: 19, Rue du Saule Trapu, Parc du Moulin de Massy, 91882 Massy Cedex, France, Telephone: 33-(1) 69 53 71 00, Fax: 33-(1) 69 53 71 10

United Kingdom: Hamamatsu Photonics UK Limited: 2 Howard Court, 10 Tewin Road, Welwyn Garden City, Hertfordshire AL7 1BW, United Kingdom, Telephone: (44) 1707-294888, Fax: (44) 1707-32577

North Europe: Hamamatsu Photonics Norden AB: Torshamnsgatan 35 16440 Kista, Sweden, Telephone: (46) 8-509-031-00, Fax: (46) 8-509-031-01

Italy: Hamamatsu Photonics Italia S.r.L: Strada della Moia, 1 int. 6, 20020 Arese (Milano), Italy, Telephone: (39) 02-93581733, Fax: (39) 02-93581741

Chian: Hamamatsu Photonics (Chian) Control No. 27 Deparations Poiling Chianz Telephones: (96) 10-6586-6006, Fax: (97) 10-6586-6006, Fax: (97

China: Hamamatsu Photonics (China) Co., Ltd.: B1201, Jiaming Center, No.27 Dongsanhuan Beilu, Chaoyang District, Beijing 100020, China, Telephone: (86) 10-6586-6006, Fax: (86) 10-6586-2866

Cat. No. KMPD1018E05 Aug. 2014 DN